Makefile

简要记录 makefile 的编写使用

更多了解:跟我一起写Makefile

makefile 主要用来简化编译运行程序的过程,以避免手动输入太长的命令

makefile 的格式

target: dependencies

[tab] command

(回车空一行)

# -----注释-----

# target 指要生成的目标程序,即编译过程的输出,如 C 语言的 a.out

# dependencies 指要所要生成目标程序的依赖,即编译过程的输入,如 test.c

# command 指编译所用到的命令,即编译过程,如 gcc test.c -o test

# [tab] 表明 command 前要用一个 tab 键,命令写完后要用回车空一行

下面以一个 gcc 编译 C 语言为例

test: test.c

gcc test.c -o test

要使用 makefile,只需在终端输入 make 或 make -f makefile_name 执行编译,就相当于一个编译过程的脚本

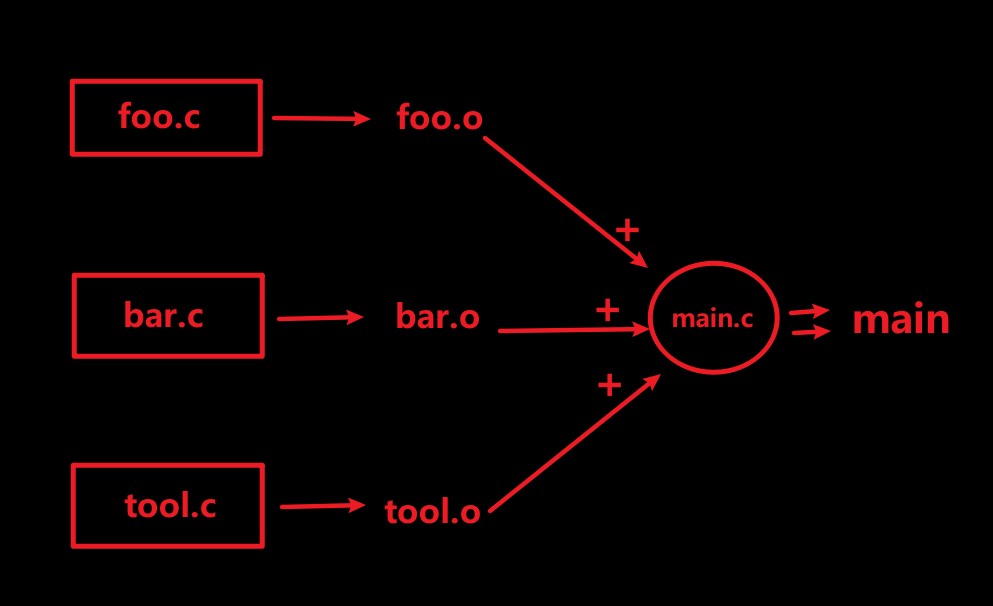

多文件编译

当一个目标程序可能需要用到多个文件,那么该如何编写呢?思路是先将所需的文件先编译,然后再将编译的结果与主程序译一起编译为最终的目标程序

通过上图,就知道了编写 makefile 的顺序,一般 makefile 的写法是从后往前写,即由果索因

main: main.c foo.o bar.o tool.o

gcc main.c foo.o bar.o tool.o -o main

foo.o: foo.c

gcc -c foo.c

bar.o: bar.c

gcc -c bar.c

tool.o: tool.c

gcc -c tool.c

clean:

rm *.o main

上面的 makefile 中的 clean 部分是当程序编译运行成功后,即可将程序打包发走,那么这些编译后的可执行文件就不需要了,即在终端可通过 make clean 命令将这些结果程序删除掉

全局变量

跟 C 语言一样,为了让 makefile 更具灵活性,允许将一些编译命令定义为全局变量,这样在后期改动时,就很省力。

CC = gcc # 定义编译器

CFLAGS = -lm -Wall -g # 定义 option

test: test.c

$(CC) $(CFLAGS) -o test.c

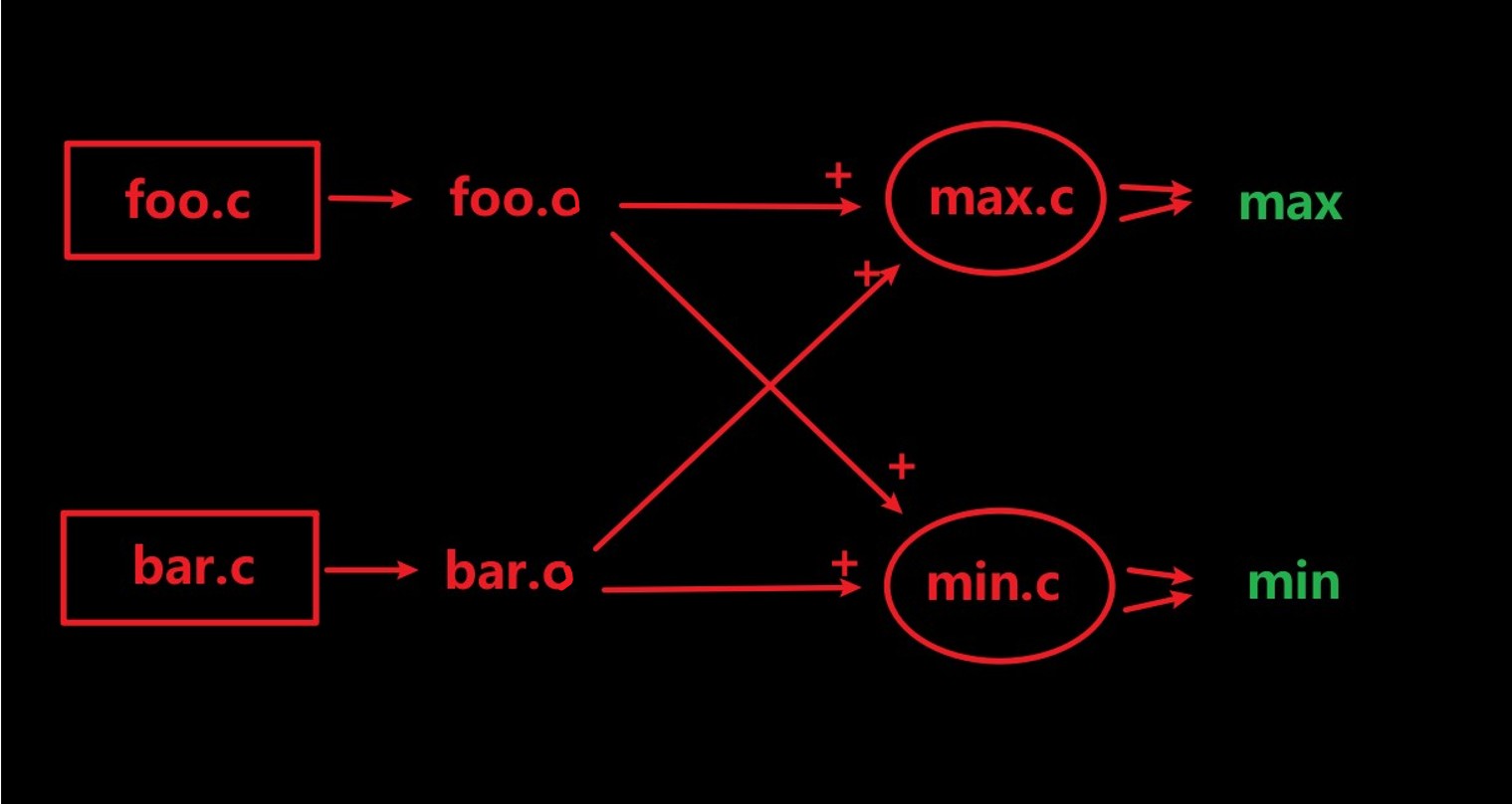

生成多个执行程序

下面将描述多个源文件编译为多个目标文件的过程

CC = gcc

CFLAGS = -lm -Wall -g

all: max min

max: max.c foo.o bar.o

$(CC) $(CFLAGS) max.c foo.o bar.o -o max

min: min.c foo.o bar.o

$(CC) $(CFLAGS) min.c foo.o bar.o -o min

foo.o: foo.c

$(CC) $(CFLAGS) -c foo.c

bar.o: bar.c

$(CC) $(CFLAGS) -c bar.c

clean:

rm *.o max min

all 让 makefile 能够编译 max 和 min,若不用 all,则 makefile 仅会执行 max 这一条编译过程,而 min 的编译会被跳过